대만으로 날아간 최태원···SK·TSMC, HBM 협력 강화HBM4부터 TSMC 활용···3D패키징도 활용할지 관심20단 쌓는 HBM4E···하이브리드 본딩 적용 가능성 ↑

AI(인공지능) 칩 시장에서 반도체 패키징에 대한 중요성이 커지자 최태원 SK그룹 회장이 SK하이닉스를 위해 지원사격에 나섰다. 지난 7일 SK그룹은 최 회장이 세계 최대 반도체 위탁생산(파운드리) 기업인 TSMC를 찾아 웨이저자 회장과 회동했다고 밝혔다. SK하이닉스와 TSMC는 두 사람의 회동 이후 고대역폭 메모리(HBM) 분야에서 협력을 강화하는 데 뜻을 모았다.

이미 양사는 올해 4월 차세대 HBM 생산과 패키징 기술 역량을 강화하기 위해 양해각서(MOU)를 체결한 바 있다. 그동안 SK하이닉스는 5세대 HBM3E까지 자체 공정으로 HBM 패키지 내 최하단에 있는 베이스 다이(Base Die)를 만들었으나 내년 양산을 예고한 6세대 HBM4부터는 TSMC의 로직(Logic) 선단 공정을 활용해 맞춤형 HBM을 생산할 계획이다. 로직 공정을 활용할 경우 연산처리 능력을 끌어올릴 수 있는 등 HBM에 다양한 기능을 추가할 수 있다는 이유에서다.

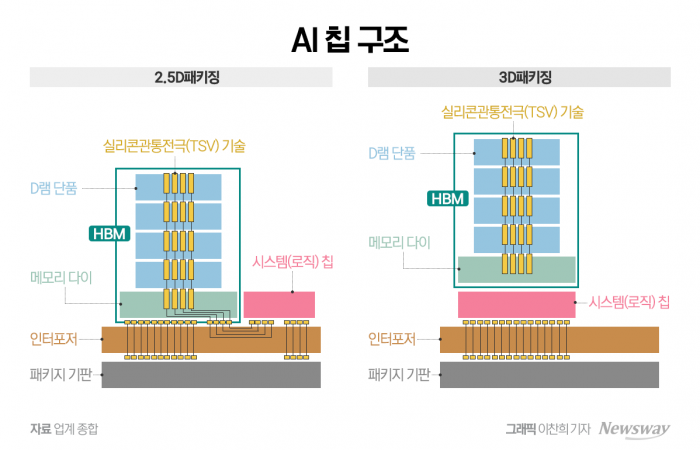

현재 글로벌 시장에서 가장 많이 쓰이는 AI 칩은 엔비디아 GPU(그래픽저장장치) 옆에 HBM을 붙여 조립한다. GPU와 HBM을 하나로 연결하기 위한 기술로는 인터포저(Interposer) 라는 특수 기판 위에 두 개의 칩을 병렬 구조로 패키징 하는 2.5D패키징이 가장 많이 쓰인다. 이 같은 공정은 TSMC의 고유 특허인 CoWoS(Chip on Wafer on Substrate)로 이뤄지기에 SK하이닉스가 TSMC와의 동맹을 강화하는 이유다.

HBM4를 활용하면 칩을 옆으로 붙이지 않고 HBM 아래에 GPU가 위치하는 3D패키징이 활용될 가능성도 제기되고 있다. 일반적으로 기존 HBM은 1024개의 I/O(데이터 전송 통로)가 구현되는데 이는 2.5D패키징으로 만들어진 AI 칩에는 정보가 들어오고 나가는 HBM 내 통로가 1024개가 있다는 뜻이다. 반면 HBM4에는 I/O가 2048개로 2배 늘어나게 되는데 반도체 업계는 3D패키징으로 GPU를 직접 연결할 경우 데이터 처리 속도가 빨라질 수 있다고 설명한다.

다만 업계 관계자는 "HBM4부터 파운드리 기업의 공정을 사용한다고 하니 칩들이 마치 하나로 연결되는 것처럼 알려져 있는데 아직 기술적인 성숙도가 올라오지 않아 앞으로도 당분간 2.5D패키징이 활용될 것"이라고 말했다.

또 차세대 HBM은 D램을 적층할 때 쓰는 패키징도 기존 공법과 다른 방식이 활용될 예정이다. SK하이닉스의 경우 오는 2026년 양산할 예정인 7세대 HBM4E부터는 하이브리드 본딩(Hybrid Bonding)을 사용할 것으로 보인다.

앞서 김귀욱 SK하이닉스 HBM선행기술팀장은 지난달 서울 광진구 그랜드워커힐 호텔에서 열린 국제메모리워크숍에서 "HBM4에선 하이브리드 본딩도 연구 중이지만 현재까진 수율(완성품 중 양품 비율)이 높지 않다"며 "고객사가 20단 이상 제품을 요구했을 때에는 두께 때문에 새로운 공정을 모색해봐야 할 수 있다"고 말했다.

SK하이닉스는 HBM4까지 MR-MUF 방식으로 D램을 쌓는다. D램 사이사이에는 칩들의 전기적 연결을 위해 형성한 전도성 돌기인 범프(Bump)가 있는데 이를 열로 녹여 칩을 잇는 과정을 리플로우(Reflow)라고 부른다. 몰디브 언더필(Molded UnderFill)은 침들이 연결된 후 방열로 인한 휨 현상을 방지하기 위해 EMC(에폭시 밀봉재) 등 보호재를 채우고 칩을 감싸는 작업을 뜻한다.

하이브리드 본딩은 범프를 없애 더 많은 칩을 쌓는 차세대 기술로 꼽힌다. HBM4는 D램을 최대 16단까지 쌓을 것으로 예상되고 있는데 HBM4E는 20단 이상으로 높여야 하기에 차세대 패키징 기술이 필요한 상황이다. HBM 등 반도체 규격은 국제반도체표준협의기구(JEDEC)에서 정한 규칙을 따라야 하기에 기업마다 칩 높이를 마음대로 정할 수가 없는데 칩 두께를 무한정 줄일 수 없는 만큼 패키징 기술이 각광받을 수밖에 없는 것이다.

관련기사

관련태그

뉴스웨이 김현호 기자

jojolove7817@newsway.co.kr

저작권자 © 온라인 경제미디어 뉴스웨이 · 무단 전재 및 재배포 금지

댓글